SOI와 실리콘 웨이퍼 비교: 반도체 프로젝트에 가장 적합한 것은 무엇일까요?

1 소개

SOI는 실리콘 층-절연층-실리콘 기판 구조의 반도체 소재입니다. 반도체 소자에 일반적으로 사용되는 실리콘 웨이퍼와 비교하면 재료 구조, 성능 특성 적용 분야 등에서 큰 차이가 있습니다.

SOI 구조는 실리콘 층-절연층-실리콘 기판의 적층 구조를 통해 소자의 성능과 신뢰성을 향상시키지만 제조 비용이 더 높습니다. 반면에 전통적인 실리콘 웨이퍼는 제조 비용이 낮고 다양한 집적 회로 제조에 적합합니다.

![]()

2 SOI란 무엇인가요?

SOI는 실리콘 온 인슐레이터의 약자입니다. SOI에서는 실리콘 칩의 표면이 절연 재료(일반적으로 이산화규소)로 덮여 있고, 그 위에 실리콘 층이 성장합니다. 이 구조는 실리콘 층-절연층-실리콘 기판의 적층 구조를 만듭니다.

2.1 SOI의 구조

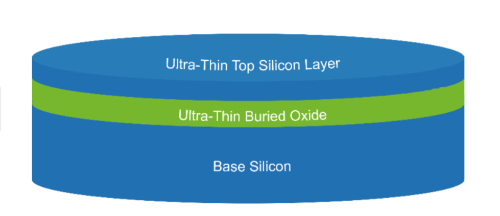

SOI(실리콘 온 인슐레이터)의 구조는 다음과 같은 주요 부분으로 구성됩니다:

- Si 레이어: SOI 구조 위에는 일반적으로 원하는 전자적 특성과 소자 특성을 갖는 실리콘(Si) 결정 층이 있습니다. 이 층은 표준 실리콘 웨이퍼 성장 기술을 사용하여 준비할 수 있습니다.

- 절연 층: Si 층 아래에는 일반적으로 이산화규소(SiO2)와 같은 절연 재료가 있습니다. 절연 층의 목적은 위의 실리콘 층을 아래의 실리콘 기판으로부터 분리하여 트랜지스터 간의 누화를 줄이는 것입니다.

- 실리콘 기판: 실리콘 기판은 SOI 구조의 하단에 위치하며 일반적으로 웨이퍼의 주요 지지 기판입니다. 실리콘 기판은 일반적으로 결정질 실리콘으로, SOI 구조에 기계적 지지력과 안정성을 제공합니다.

2.2 SOI의 분류

SOI 기술에는 여러 가지 변형이 있습니다. SOI는 구조와 목적에 따라 다양한 기준에 따라 분류할 수 있습니다.

2.2.1 구조 유형별 분류

공통 SOI(c-SOI): 공통 SOI는 가장 일반적인 SOI 구조 중 하나로, 풀 SOI라고도 하며 실리콘 웨이퍼 표면에 절연층(보통 이산화규소)을 증착한 다음 그 위에 실리콘 층을 성장시키는 일반적인 SOI 제조 방법을 사용합니다. 일반적인 SOI에서 실리콘 층의 두께는 일반적으로 절연 층의 두께와 비슷하여 실리콘 층-절연 층-실리콘 기판 구조를 형성합니다.

부분 SOI(p-SOI): 부분 SOI는 실리콘 층의 두께가 절연 층 두께의 일부에 불과할 정도로 더 얇다는 점에서 일반 SOI와 다릅니다. 부분 SOI에서 실리콘 층의 두께는 일반적으로 절연 층의 두께보다 작기 때문에 부분 SOI 구조의 실리콘 층이 더 얇아집니다.

리버스 SOI(r-SOI): 리버스 SOI는 일반 SOI 및 부분 SOI와는 다른 특수한 SOI 구조입니다. 리버스 SOI에서는 실리콘 층이 기판에서 제거되고 절연 층에 다시 부착됩니다. 이 구조는 트랜지스터가 절연층 위에 위치하고 실리콘 기판이 절연층 아래에 위치하도록 하여 기존 SOI 구조의 토폴로지를 변경합니다.

이러한 다양한 SOI 변형은 특정 애플리케이션에서 다양한 장점과 적용 가능성을 제공합니다. 일반적인 SOI는 고성능 및 저전력 애플리케이션에 일반적으로 사용되는 반면, 부분 SOI는 일부 특정 무선 주파수(RF) 장치 제조에 더 적합하며 인버티드 SOI는 고속, 저손실 장치와 같은 특정 애플리케이션에서 추가적인 이점을 제공합니다.

2.2.2 크리스탈 기판 유형별 분류

실리콘-온-인슐레이터(SIMOX-SOI): SIMOX(산소 주입에 의한 분리)는 실리콘-온-인슐레이터라고도 하는 일반적인 SOI 제조 방법입니다. SIMOX-SOI 제조에서는 산소 이온을 웨이퍼에 주입한 다음 열처리하여 산소 이온이 웨이퍼에 실리콘 산화물의 절연 층을 형성하여 SOI 구조가 형성되도록 합니다.

초박형 SOI(UTSOI): 초박형 SOI는 일반적으로 수 나노미터에서 수십 나노미터 사이의 매우 얇은 실리콘 층이 특징인 특수한 유형의 SOI 구조입니다. UTSOI의 제조 방법에는 일반적으로 실리콘 기판 위에 매우 얇은 실리콘 층을 형성하기 위해 특수 성장 또는 박리 기술을 사용하여 SOI 구조를 구현합니다.

에피택셜 SOI(Epi-SOI): Epi-SOI는 실리콘 기판 위에 에피택셜 실리콘 층을 성장시켜 SOI 구조를 형성하는 방식입니다. Epi-SOI에서 에피택셜 실리콘 층은 실리콘 기판 위에 성장되며 일반적으로 기판과 동일한 결정 구조를 가지지만 실리콘 층과 기판 사이에 절연 층이 있습니다.

SIMOX-SOI는 일반적으로 IC 제조에 사용되고, UTSOI는 모바일 통신 및 RF 장치와 같은 고성능 및 저전력 애플리케이션에 일반적으로 사용되며, Epi-SOI는 특정 장치 제조 요구에 맞는 더 나은 결정 품질과 구조 제어를 제공합니다.

2.2.3 실리콘 층의 두께에 따른 분류

박막 SOI: 박막 SOI에서 실리콘 층의 두께는 일반적으로 수십 나노미터에서 수백 나노미터 사이입니다. 이러한 유형의 SOI 구조는 저전력 전자 장치, 광전자 장치 등과 같은 초박형 장치를 제작하는 데 자주 사용됩니다. 박막 SOI는 일반적으로 화학적 기계적 연마(CMP), 수소 이온 주입 및 박리 등의 기술을 포함한 일련의 정밀 처리 단계를 사용하여 제조됩니다.

후막 SOI: 후막 SOI에서 실리콘 층의 두께는 일반적으로 수백 나노미터 이상입니다. 이러한 유형의 SOI 구조는 일반적으로 마이크로프로세서, 메모리 등과 같은 전통적인 집적 회로 장치를 제작하는 데 사용됩니다. 후층 SOI는 일반적으로 SIMOX, 유니본드, 스마트 컷과 같은 다양한 기술을 사용하여 준비됩니다. 이러한 기술을 사용하면 기존 집적 회로 제조의 요구 사항을 충족하는 두꺼운 두께의 실리콘 층을 준비할 수 있습니다.

2.2.4 트랜지스터의 전하 제어 방법에 따른 분류

완전 공핍형 SOI(FD-SOI): FD-SOI에서는 전체 실리콘 층이 공핍된 상태이므로 트랜지스터의 전하가 위의 게이트에 의해 완전히 제어되고 하단 기판의 영향을 받지 않습니다. 실리콘 층의 두께와 절연 층의 특성을 정밀하게 제어함으로써 전체 실리콘 층을 공핍 상태로 만들 수 있습니다. 이 구조는 더 나은 전하 제어와 낮은 누설 전류를 제공합니다. 완전 공핍형 SOI는 더 높은 성능과 낮은 전력 소비를 가진 차세대 반도체 기술로 평가받으며 칩 설계 및 제조 분야에서 점점 더 많은 관심을 받고 있습니다.

부분 공핍형 SOI(pFD-SOI): 부분 고갈 SOI는 실리콘 층의 일부가 고갈된 상태인 반면 다른 부분은 고갈되지 않은 상태로 유지됩니다. 일반적으로 적절한 설계와 공정을 통해 실리콘 층의 일부(일반적으로 상단 부분)만이 고갈된 상태임을 구현할 수 있습니다. 부분적으로 고갈된 SOI는 모바일 통신, 무선 주파수(RF) 장치 및 기타 분야와 같은 고성능 및 저전력 애플리케이션에 사용할 수 있습니다. 더 나은 충전 제어 및 성능 최적화를 위한 기회를 제공합니다.

아래 표는 다양한 SOI 구조, 정의 특성 및 일반적인 애플리케이션을 보여 주며 각 유형 간의 차이점에 대한 포괄적인 개요를 제공합니다.

Stanford Advanced Materials (SAM) 및 기타 신뢰할 수 있는 공급업체는 다양한 크기와 유형의 SOI 웨이퍼를 제공합니다. 이러한 선택은 고객의 정확한 사양을 충족하도록 맞춤화되어 있습니다.

표 1 다양한 유형의 SOI 웨이퍼 비교

|

분류 |

유형 |

간략한 설명 및 응용 분야 |

|

구조 유형 |

c-SOI |

절연층과 유사한 실리콘 층 두께. 고성능, 저전력 애플리케이션에 사용됩니다. |

|

p-SOI |

절연층에 비해 실리콘 층이 더 얇습니다. 특정 RF 디바이스 제작에 적합합니다. |

|

|

r-SOI |

절연층 위에 실리콘 층을 다시 부착하여 구조를 반전시켰습니다. 고속, 저손실 디바이스에 적합합니다. |

|

|

크리스탈 기판 유형 |

SIMOX-SOI |

산소 이온이 실리콘 산화물 절연층을 형성합니다. IC 제조에 일반적입니다. |

|

UTSOI |

모바일 및 RF 장치와 같은 고성능, 저전력 애플리케이션을 위한 초박형 실리콘 층입니다. |

|

|

Epi-SOI |

더 나은 결정 품질이 필요한 디바이스를 위해 실리콘 기판 위에 성장된 에피택셜 층입니다. |

|

|

실리콘 층의 두께 |

박막 SOI |

수십~수백 나노미터 두께의 실리콘 층. 저전력 전자 및 광전자 장치에 적합합니다. |

|

후막 SOI |

수백 나노미터 두께의 실리콘 층. 마이크로프로세서와 같은 기존 IC 장치에 사용됩니다. |

|

|

트랜지스터의 전하 제어 방법 |

FD-SOI |

전하 제어를 위해 실리콘 층 전체가 공핍된 방식. 고성능, 저전력 차세대 기술을 목표로 합니다. |

|

pFD-SOI |

부분 실리콘 층 공핍. 고성능, 저전력 애플리케이션(예: 모바일, RF)에 적용. |

3 SOI와 실리콘 웨이퍼, 어느 것이 더 낫나요?

실리콘 온 인슐레이터(SOI) 기술과 기존 실리콘 웨이퍼는 각각 고유한 구조적 특성과 성능으로 오랫동안 반도체 제조 환경을 형성하는 데 중추적인 역할을 해왔습니다. 더 효율적이고, 더 빠르고, 더 작은 전자 기기에 대한 수요가 증가함에 따라 이 두 가지 기본 재료의 차이점을 이해하는 것이 중요해지고 있습니다. 이 비교에서는 SOI와 실리콘 웨이퍼의 구조적 뉘앙스와 성능 결과를 강조하고자 합니다.

3.1 SOI와 실리콘 웨이퍼의 구조적 차이점

실리콘 웨이퍼: 기존 실리콘 웨이퍼는 단일 실리콘 결정과 단결정 실리콘 구조로 구성됩니다. 기존 실리콘 웨이퍼에서 웨이퍼 표면은 일반적으로 추가 절연층이 없는 단결정 실리콘입니다. 실리콘 웨이퍼는 구조가 단순하며 반도체 디바이스의 가장 일반적인 기판입니다.

SOI: SOI 구조에서 실리콘 웨이퍼의 표면은 절연 재료(보통 이산화규소)로 덮여 있습니다. 이 절연 재료 층은 일반적으로 실리콘 기판에서 실리콘 층을 분리하여 디바이스 간의 누화를 줄이고 디바이스 성능과 신뢰성을 향상시키는 데 사용됩니다. 절연층 위에 또 다른 실리콘 층을 성장시켜 실리콘 층-절연층-실리콘 기판의 층 구조를 형성합니다. 실리콘 층은 트랜지스터의 활성층이며 일반적으로 원하는 전자 특성과 디바이스 성능을 갖습니다. 절연층의 두께는 소자의 특성과 성능을 제어하기 위해 애플리케이션 요구 사항에 따라 조정할 수 있습니다.

SOI는 기존 실리콘 웨이퍼에 비해 추가적인 절연층이 있습니다. 이 절연층이 있으면 디바이스 성능과 신뢰성이 향상되지만 제조의 복잡성과 비용이 증가합니다.

3.2 SOI와 실리콘 웨이퍼의 성능 차이점

- 누화 억제: SOI 구조의 각 트랜지스터는 절연층으로 분리되어 있어 디바이스 간 누화 효과를 크게 줄입니다. 절연층이 존재하기 때문에 트랜지스터 간의 전자기 결합 효과가 감소하여 장치의 성능과 신뢰성이 향상됩니다. 누화는 일반적으로 고밀도 집적 회로에서 심각한 문제이며, SOI를 사용하면 누화가 디바이스 성능에 미치는 영향을 효과적으로 줄일 수 있습니다.

- 속도 및 전력 이점: SOI 디바이스는 일반적으로 더 빠른 속도와 낮은 전력 효율을 제공합니다. SOI 구조에서 전하 이동에 대한 저항이 감소하기 때문에 실리콘 층의 전자가 더 빠르게 이동할 수 있어 스위칭 속도가 빨라지고 전력 소비가 낮아집니다. 따라서 SOI는 모바일 통신 및 고성능 컴퓨팅과 같은 고성능 및 저전력 애플리케이션에서 확실한 이점을 제공합니다.

- 향상된 내방사선성: SOI 구조는 디바이스의 내방사선 저항을 개선하여 고방사선 환경의 애플리케이션에 더 적합합니다. 절연층이 있기 때문에 SOI 장치는 방사선에 덜 민감하므로 우주, 원자력 발전소 및 기타 고방사선 환경의 전자 장치에 광범위하게 응용할 수 있습니다. 향상된 내방사선성은 우주 항공 및 원자력 에너지와 같은 일부 특정 애플리케이션에 매우 중요합니다.

3.3 SOI 및 실리콘 웨이퍼의 사용 방법

--SOI 응용 분야

고성능 애플리케이션: SOI는 고속 컴퓨터 칩 및 그래픽 프로세서와 같이 고성능이 필요한 애플리케이션에 자주 사용됩니다. 낮은 충전 동작 임피던스와 누화 억제 특성으로 고성능을 구현하는 데 이상적입니다.

저전력 애플리케이션: SOI 장치는 전력 소비가 낮고 스위칭 속도가 빠르기 때문에 저전력 소비가 필요한 모바일 장치 및 무선 센서 네트워크와 같은 분야에서 광범위하게 응용할 수 있습니다. 예를 들어 스마트폰이나 태블릿 PC와 같은 디바이스의 칩은 종종 SOI 기술을 활용합니다.

무선 주파수(RF) 애플리케이션: SOI는 빠른 속도와 낮은 손실 특성으로 무선 주파수(RF) 애플리케이션에서 큰 이점을 제공합니다. 예를 들어, SOI 디바이스는 고성능 RF 프런트 엔드 모듈, 안테나 스위치, 전력 증폭기 등을 제작하는 데 사용할 수 있습니다.

고방사선 환경에서의 애플리케이션: SOI 구조는 디바이스의 내방사선성을 향상시켜 우주, 원자력 발전소 및 기타 고방사선 환경에서의 애플리케이션에 중요합니다. 예를 들어 우주 탐사선, 위성 통신 시스템 및 고방사선 환경에서 작동해야 하는 기타 장치는 종종 SOI 기술을 사용합니다.

--기존 실리콘 웨이퍼 애플리케이션

기존 실리콘 웨이퍼는 마이크로프로세서, 메모리, 센서 등 다양한 집적 회로를 제조하는 데 널리 사용됩니다. 실리콘 웨이퍼는 집적 회로(IC) 제조의 기초입니다. 마이크로프로세서, 메모리, 아날로그 회로, 디지털 회로 등 다양한 종류의 IC는 실리콘 웨이퍼 위에 다양한 재료와 회로를 적층하여 제조됩니다. 개인용 컴퓨터, 가전제품, 자동차 전자 시스템 등 거의 모든 전자 기기에서 전통적인 실리콘 웨이퍼 제조 칩을 사용합니다. 또한 산업 분야, 태양 전지, 바이오 의료 기기 등 일반적으로 사용되는 다양한 전자 기기를 제조하는 데에도 사용할 수 있습니다. 실리콘 웨이퍼는 우수한 반도체 특성뿐만 아니라 성숙한 생산 공정과 안정적인 품질 관리로 인해 생산 및 연구 공정에서 널리 사용되고 있으며, 기술 문턱도 SOI에 비해 낮습니다.

3.4 SOI 및 실리콘 웨이퍼 생산 방법

--SOI 결정 준비 방법

3.4.1 SIMOX 기술

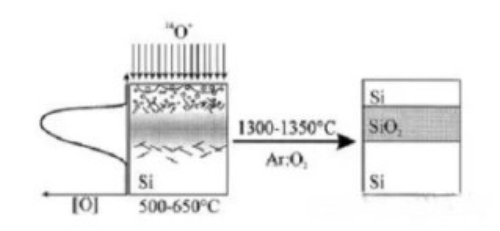

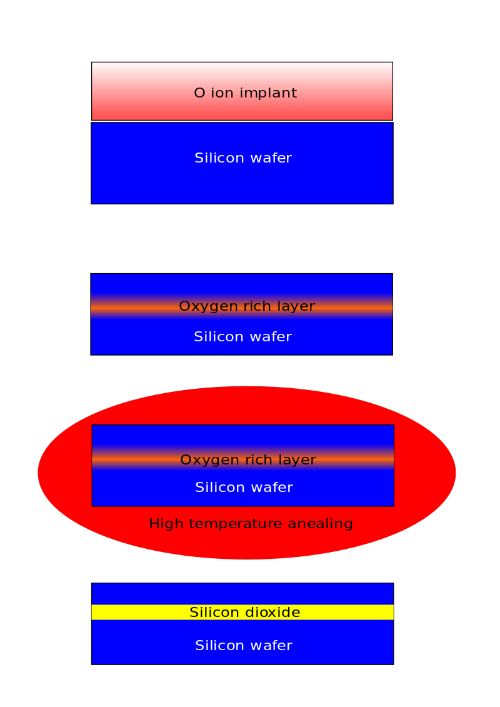

산소 주입에 의한 분리의 줄임말인SIMOX 기술은 SOI(실리콘-온-인슐레이터) 웨이퍼를 제조하는 선구적인 방법 중 하나입니다. 이 기술은 이온 주입을 활용하여 실리콘에 산소 이온을 도입하여 매립 산화물 분리층을 형성합니다. 이 매립 산화물 층은 기판을 상단 실리콘 박막 층으로부터 효과적으로 분리합니다. 이 공정에는 일반적으로 200keV의 에너지 수준과 1.8 × 10^18 cm^-2의 선량으로 표면 아래의 실리콘 웨이퍼에 산소 이온을 주입하는 과정이 포함됩니다. 그 후 1350°C에서 3~6시간 동안 지속되는 고온 어닐링 공정은 웨이퍼 내의 산소 이온과 실리콘 원자 간의 화학 반응을 촉진하여 표면 아래에 두께가 240nm 미만인 이산화규소 절연층을 형성합니다. 이 절연층 위에 결정질 실리콘 층이 형성되어 실리콘 박막-이산화규소 절연층-실리콘 기판으로 구성된 SOI 구조가 완성됩니다.

SIMOX 기술의 장점은 비교적 균일한 BOX(Buried Oxide) 층을 형성한다는 점입니다. 사출 에너지를 관리하여 BOX 상단의 실리콘 층 두께를 정밀하게 제어할 수 있습니다. 또한 BOX와 상단 실리콘 층 사이의 인터페이스는 매우 평탄하게 유지됩니다.

하지만 SIMOX 기술에도 한계가 있습니다. BOX와 상단 실리콘 층의 두께를 조절할 수 있는 범위가 상대적으로 제한적입니다. 지나치게 얇은 층은 기생 커패시턴스 증가와 함께 상단층과 기판 사이의 단절을 초래할 수 있기 때문에 일반적으로 BOX 두께는 240nm를 초과하지 않습니다. 마찬가지로, 상단 실리콘 필름 두께는 일반적으로 300nm로 제한되므로 비용이 많이 드는 에피택셜 실리콘 성장과 후속 화학적 기계적 연마(CMP) 평탄화 처리가 필요합니다. 또한 SIMOX는 표면 필름 손상을 유발할 수 있으며, 상단 실리콘 필름의 결정 품질이 벌크 단결정 실리콘의 결정 품질과 일치하지 않을 수 있습니다. 또한, 매립된 SiO2의 결정 품질은 열 산화를 통해 얻은 결정 품질보다 떨어집니다. SIMOX를 구현하려면 장시간의 고온 어닐링 공정과 함께 고가의 대형 빔 흐름 산소 주입기와 같은 특수 이온 주입 장비가 필요하므로 생산 비용이 높아집니다.

3.4.2 BESOI 기술

BESOI(본드 앤 에칭 백 실리콘-온-인슐레이터) 기술은 두 웨이퍼를 서로 밀접하게 접착하여 그 사이에 매립 산화물 층으로 이산화규소 층을 생성하는 기술입니다. 그 후, 백 인그레이빙 기술을 사용하여 웨이퍼 한 장의 두께를 정밀하게 조정하여 SOI 웨이퍼에 원하는 두께를 형성합니다.

BESOI 공정은 한 웨이퍼(웨이퍼 A)를 열 산화 처리하여 산화물 층을 생성하고 다른 웨이퍼(웨이퍼 B)는 산화 처리된 웨이퍼 A의 표면과 저온 결합하는 것으로 시작되며, 실리콘 융합 본딩(SFB)으로 알려진 이 결합 공정은 여러 단계로 이루어집니다:

친수성 처리: 두 웨이퍼 모두 저온(400°C) 친수성 처리를 통해 표면에 수산화(OH) 결합 형성을 유도합니다.

반데르발스 힘을 통한 결합: 그런 다음 두 웨이퍼를 접촉시키고 OH 결합이 반데르발스 힘을 통해 결합을 촉진합니다.

열 어닐링: 고온(1100°C) 열 어닐링으로 수소 이온을 제거하여 결합된 계면에서 Si-O-Si 결합의 형성을 촉진하여 결합을 강화합니다.

백 에칭: 백 에칭 기술을 사용하여 한 웨이퍼에서 과도한 실리콘을 제거하여 상단 실리콘 박막에 원하는 두께를 남깁니다. 이후 어닐링과 화학적 기계적 연마(CMP)를 통해 SOI 웨이퍼에 매끄럽고 깨끗한 표면을 형성합니다.

BESOI 기술은 SIMOX 기술에 비해 몇 가지 장점이 있습니다. 예를 들어, 사출 손상과 관련된 문제를 방지하고 결함 밀도와 핀홀 밀도가 낮은 열 산화 매립 산화물 층의 형성을 보장합니다. 또한 BESOI를 통해 생산된 상단 실리콘 필름은 고품질 단결정 실리콘으로 구성되어 전반적인 디바이스 성능을 향상시킵니다.

하지만 BESOI 기술에도 도전 과제가 있습니다. 매우 얇은 상단 실리콘 필름을 만드는 것이 어렵고, 인터페이스 결함 및 상단 실리콘 필름의 균질성을 제어하는 것이 여전히 어려운 과제입니다. 또한 이 공정에는 고비용의 후면 식각 및 CMP 단계가 포함되므로 웨이퍼 재료 낭비가 상당하며, 이는 재활용이 불가능하고 생산 비용 상승에 기여합니다.

3.4.3 스마트 컷 기술

Smart-Cut 기술은 BESOI에서 파생된 기술입니다: 두 개의 실리콘 웨이퍼를 먼저 준비하고, 웨이퍼 중 하나를 열 산화하여 SiO2 층을 형성한 다음 수소 이온을 웨이퍼 기판에 주입하고, 다른 웨이퍼는 처리할 필요가 없으며, BESOI와 마찬가지로 두 웨이퍼를 서로 결합합니다; 결합 후 수소 이온이 주입된 웨이퍼는 400~600°C에서 열 반응에 의해 수소 이온이 풍부한 계면에서 깨지고, 마지막으로 깨진 표면과 산화물 층 사이의 계면은 고온 처리(1100°C) 후 실리콘 필름 층을 형성하여 수소 이온을 밀어냅니다. 접합 후 수소 이온이 주입된 웨이퍼는 수소 이온 농축 지점에서 파단되고 파단 표면과 산화물 층 사이에 실리콘 박막층이 형성되며, 마지막으로 고온 처리(1100°C) 후 수소 이온을 몰아내어 접합된 계면이 Si-O-Si 결합을 형성하여 화학 결합을 강화하고 실리콘 박막층의 품질을 개선한 후 CMP 처리로 표면을 평평하게 만듭니다.

Smart-Cut은 상단 실리콘 필름이 벌크 실리콘이고 BOX가 열 산화 필름이라는 점에서 BESOI와 유사합니다. BOX층과 상단 실리콘막의 두께를 넓은 범위에서 조절할 수 있으며, 이온 주입 에너지를 활용하여 상단 실리콘막의 두께를 제어함으로써 매우 얇은 두께와 우수한 균일도를 가진 상단 실리콘막을 얻을 수 있습니다. 또한 박리된 웨이퍼 소재를 재사용할 수 있어 비용 절감 효과도 기대할 수 있습니다.

--실리콘 웨이퍼 결정 준비 방법

조크랄스키 방법은 실리콘 결정 성장에 널리 사용되는 방법으로, 1685°C의 온도를 유지하도록 가열된 실리콘으로 채워진 도가니를 활용합니다. 이 온도는 실리콘의 녹는점보다 약 100°C 높은 온도로, 도가니 안의 실리콘을 녹입니다. 도가니의 상단에는 리프팅로드가 위치하며, 이 리프팅로드는 자유롭게 들어 올리고 회전할 수 있는 기계 장치가 있습니다. '씨앗' 역할을 하는 작은 단결정 실리콘 조각이 지렛대 위에 부착되어 있습니다. 이 씨앗 결정은 주변의 실리콘 원자를 끌어당겨 결정 구조로 조직화합니다. 결정이 서서히 상승하고 회전하면서 추출된 부분은 동일한 단결정의 일부로 남게 됩니다. 이렇게 만들어진 대형 단결정은 직경이 최대 200밀리미터에 달하며, 평균 팔보다 두껍습니다. 이 결정은 인터페이스나 결함이 없어 인간이 만든 단결정에서 얻을 수 있는 최고의 완벽함을 보여줍니다.

재료 순도를 보장하고 불균일한 핵 형성을 방지하기 위해 모든 작업은 진공 또는 불활성 가스 보호 상태에서 이루어져야 합니다. 기존의 단결정 실리콘 리프팅 기술은 결정 전위를 방지하기 위해 결정 성장이 시작될 때 '넥킹 방법'이라고 불리는 얇은 목을 형성하는 방법을 사용했습니다. 그러나 시딩 기술의 발전, 특히 상당량의 붕소를 시드 결정에 주입하는 기술이 발전하면서 강도가 크게 강화되어 직경 3mm의 목이 필요하지 않게 되었습니다. 이 혁신적인 접근 방식은 30년 된 넥킹 방식을 대체하여 대형 단결정 실리콘 생산을 촉진할 뿐만 아니라 결정 성장 시간을 단축하고 수율을 향상시켜 초대형 집적 회로를 비용 효율적으로 생산할 수 있는 가능성을 열어주었습니다.

웨이퍼 성장에서는 폴리실리콘을 용광로 내의 석영 도가니에 투입한 후 진공 또는 불활성 가스를 퍼지하여 용융 상태를 만듭니다. 용융된 실리콘이 안정화되면 액체 표면에서 미리 결정된 시드 크리스탈의 내부 결정 방향을 가이드로 사용하여 단결정을 끌어낼 수 있습니다. 도가니 액체 표면 높이, 고액 계면 온도, 시드 크리스탈 회전 속도를 정밀하게 제어하여 실리콘을 액체에서 다시 고체로 변환하여 대경 단결정의 성장을 위한 균일한 내결정 방향을 보장합니다. 컴퓨터로 제어되는 자동 조정 공정과 리프팅 속도는 등방성 단결정 실리콘 성장을 보장합니다.

표 2 SOI 웨이퍼와 실리콘 웨이퍼 비교

|

실리콘 웨이퍼 |

SOI 웨이퍼 |

||

|

구조 |

절연층 없음 |

절연 층 |

|

|

성능 |

누화 억제 |

아니요 |

예 |

|

속도 및 전력 |

더 낮게 및 더 높게 |

더 높고 낮음 |

|

|

방사선 저항 |

낮음 |

더 높음 |

|

|

애플리케이션 |

집적 회로 |

고성능 애플리케이션 |

|

|

태양 전지 |

저전력 애플리케이션 |

||

|

생체 의료 기기 |

고방사선 환경 |

||

|

준비 및 비용 |

조크랄스키 방법 |

SIMOX/BESOI/스마트 컷 |

|

|

편리함 |

복잡함 |

||

|

저렴한 비용 |

높은 비용 |

||

4 결론

재료 구조, 성능 특성 적용 분야 등의 측면에서 SOI와 실리콘 웨이퍼에는 상당한 차이가 있습니다. SOI 구조는 실리콘 층-절연층-실리콘 기판 구조를 통해 디바이스 성능과 신뢰성을 향상시키지만 제조 비용이 더 높습니다. 이에 비해 전통적인 실리콘 웨이퍼 제조는 비용이 저렴하고 다양한 집적 회로 제조에 적합합니다. 따라서 재료 구조를 선택할 때는 특정 애플리케이션 요구 사항과 비용 고려 사항을 바탕으로 SOI와 실리콘 웨이퍼의 장단점을 종합적으로 평가하여 최상의 성능과 경제적 이점을 달성해야 합니다.

관련 자료

실리콘 웨이퍼 품질이 반도체 성능 및 신뢰성에 미치는 영향

참고 문헌

[1]Jin W ,Wei C ,Wanghua Z , 외. SiN 및 SOI 플랫폼에서 접힌 도파관을 사용한 열광 위상 시프터의 최적화 및 종합적인 비교[J]. 옵틱스 커뮤니케이션즈,2024,555.

[2]Xin F ,Jiaqi N ,Shanglin Y , 외. SOI 플랫폼에서 조정 가능한 중심 파장 및 재구성 가능한 자유 스펙트럼 범위를 가진 광학 노치 필터[J]. Optics Communications,2024,554.

[3]N. V ,A. M ,I. K , 외. SOI에서 질화규소 저항성 메모리의 새로운 크로스바 어레이는 멤리스터 배급 로직을 가능하게 합니다[J]. 솔리드 스테이트 일렉트로닉스,2024,211.

바

바

비즈 & 구체

비즈 & 구체

볼트 및 너트

볼트 및 너트

도가니

도가니

디스크

디스크

섬유 및 원단

섬유 및 원단

영화

영화

플레이크

플레이크

폼

폼

호일

호일

과립

과립

벌집

벌집

잉크

잉크

라미네이트

라미네이트

덩어리

덩어리

메시

메시

메탈라이즈드 필름

메탈라이즈드 필름

플레이트

플레이트

파우더

파우더

Rod

Rod

시트

시트

단결정

단결정

스퍼터링 타겟

스퍼터링 타겟

튜브

튜브

워셔

워셔

전선

전선

변환기 및 계산기

변환기 및 계산기

Chin Trento

Chin Trento