2025 스탠포드 첨단 재료 대학 장학금 수상자 발표

2025 스탠포드 어드밴스드 머티리얼즈 대학 장학금 수상자를 발표하게 되어 기쁘게 생각합니다:

브람두타 딕싯

미네소타 대학교 트윈 시티

전기 및 컴퓨터 공학부, 박사과정 3학년 학생

딕싯의 연구는 텅스텐, 탄탈륨, 니오븀을 기반으로 한 새로운 설계를 제안하여 스핀 궤도 토크(SOT) 반도체 소자의 효율을 개선하고 임계 전류 밀도를 낮추는 방법을 제공합니다. 그의 연구는 미래의 고성능, 저전력 전자 장치 개발에 귀중한 통찰력을 제공합니다.

스탠포드 어드밴스드 머티리얼즈 대학 장학금은 재료 연구 및 응용 분야에서 탁월한 혁신과 지적 능력을 입증한 뛰어난 젊은 학자에게 수여됩니다. 브람두타 딕싯의 수상을 진심으로 축하하며, 동시에 모든 지원자들에게도 진심으로 감사의 인사를 전합니다. 많은 저명한 학자들의 열정적인 참여 덕분에 선발 과정 자체가 재료 과학의 흥미로운 미래를 엿볼 수 있는 수준 높은 학술 교류의 장이 되었습니다.

장학금 프로그램과 향후 기회에 대한 자세한 내용은 여기를 클릭하세요.

수상 프로젝트:

우승자의 원본 제출물: 브람두타_딕싯_스탠포드_첨단_재료_장학금_2025_Submission.pdf

희소 금속 스핀트로닉스: 결정론적 MRAM을 위한 Ni₄W에서 TaIrTe₄/NbIrTe₄ 저대칭 플랫폼으로의 전환

초록:

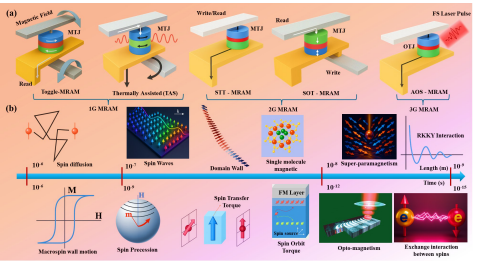

스핀트로닉스는 전하 제어를 넘어 데이터를 저장하는 물리학이 풍부한 매혹적인 분야입니다. 스핀트로닉스는 전자의 스핀을 활용하여 내구성이 높고 에너지 소모가 적으며 지연 시간이 짧은 비휘발성 메모리(NVM)를 개발합니다. 그림 1과 같이 다양한 세대의 MRAM과 스위칭 메커니즘[1] 중에서 업계에서 채택하는 자기 랜덤 액세스 메모리(MRAM)에는 스핀 전달 토크(STT)와 스핀 궤도 토크(SOT)라는 두 가지 주요 클래스가 있습니다. STT-MRAM은 읽기 및 쓰기에 동일한 경로를 사용하기 때문에 역사적으로 내구성이 제한적이고 비트 오류율이 높다는 단점이 있었습니다. 반면 SOT-MRAM은 읽기 경로와 쓰기 경로를 분리하여 이러한 문제를 완화합니다. SOT-MRAM에는 스핀 궤도 결합(SOC)을 생성하는 중금속 채널이 있으며, 희소금속 지원 SOT 장치는 차세대 NVM 및 확률론적/AI 하드웨어를 위한 초저에너지, 필드 없는 자기 스위칭을 약속합니다.

현재 저는Ni4W, PtW(합금)와 같은 다양한 저대칭 중금속과TaIrTe₄ 및 NbIrTe₄와 같은 저대칭 희귀 반금속 칼코게나이드에 중점을 두고 연구하고있습니다. 높은 SOC, 큰 일함수, 풍부한 계면 화학적 특성으로 인해 SOT MRAM의 결정론적 스위칭을 달성하는 데 도움이 됩니다.

그림 1: (a) MRAM의 세대별 환경: 토글, STT, 열 지원, SOT 및 광학 지원 아키텍처. (b) 해당 동역학 영역: fs-ps(초고속 자화, 스핀 이완, 일관된 전이), ps-ns(스핀 토크), ns-µs(도메인 벽 동역학 및 STT), 그 이상(열 효과 및 자기 유지) [1].

이를 기반으로 산업 호환 마그네트론 스퍼터링을 사용하여 고품질 에피택셜 Ni₄W 박막을 성장시켰으며, 최근 Advanced Materials에발표된 이 연구에서 0.73의 높은 SOT 효율을 보고했습니다 . 이제 이를 확장하여 텅스텐 화학량론 제어를 통해 Ni₄W의 페르미 레벨 튜닝과 Ni4W의 코발트 도핑을 통해 전자 상태를 스핀 홀 전도도(SHC)의 피크와 정렬하여 SOT 효율을 향상시키고 임계 전류 밀도를 낮추는 것을 목표로 하고 있습니다. 이와 동시에 박리된 TaIrTe₄ 및 NbIrTe₄ 2D 플레이크 기반 홀바 소자를 제작하여 기존의 스핀 편광 및 게이트 제어 가능 스위칭을 위해 고유한 낮은 대칭성을 활용합니다.

기사

텅스텐(W), 탄탈륨(Ta), 니오븀(Nb) 과 같은 희귀 금속은 오늘날 가장 유망한 스핀트로닉 기반 SOT-MRAM으로 주목받고 있습니다. 이러한 무거운 원소들은 퍼멀로이(Py) 및 CoFeB와 같은 초박형 강자석 옆에 배치되면 강력한 SOC를 통해 전하 전류를 횡방향 스핀 전류로 변환합니다. 분극화된 주입된 스핀은 자석의 상태를 변화시킬 수 있으며, 이것이 SOT 메모리의 기본 원리입니다. 낸드 플래시와 같은 기존의 CMOS 기반 NVM에 비해 SOT 디바이스는 비휘발성, 나노초급 쓰기, 비트당 초저전력으로 캐시형 MRAM, 에지 AI 가속기, 확률론적 인메모리 컴퓨팅에 적합합니다.

(1) 빠른 스위칭에 필요한 임계 전류 밀도(Jc)와 (2) 수직 자기 이방성(PMA) 디바이스에서 대칭을 깨는 데 필요한 외부 자기장이라는 두 가지 주요 문제로 인해 SOT-MRAM의 광범위한 배포가 제한되었습니다. 이 글에서는 Ni₄W와 저대칭 웨이일 반도체(TaIrTe₄ 및 NbIrTe₄)가 앞서 언급한 문제를 직접 해결하는 방법을 설명하고, 현재 진행 중인 여러 프로젝트의 실험 로드맵을 간략하게 설명하겠습니다. 마지막으로 제 연구가 재료 과학에서 소자 제작 및 산업 응용에 이르는 전체 스펙트럼을 어떻게 연결하고 다루는지에 대해 이야기하겠습니다.

1) 대칭성 파괴 기능이 내장된 Ni₄W 기반 SOT 소스:

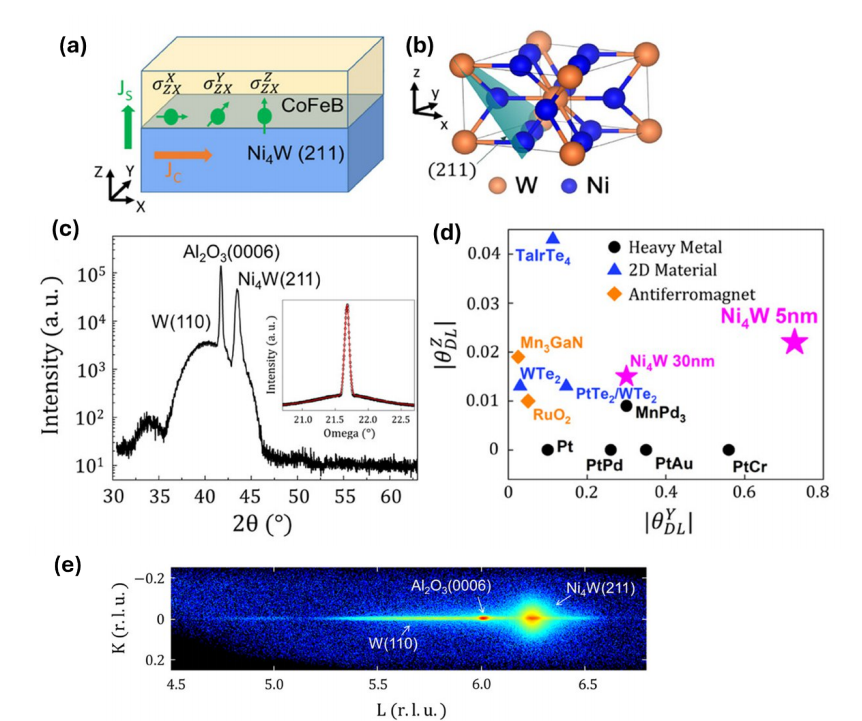

그림 2에 표시된 최근 연구( Advanced Materials Journal1면에 게재 )[2,3]에서 우리는 Ni₄W가 텅스텐이 풍부한 금속 간 금속이라는 것을 발견했습니다. 저대칭 결정 배향은 다방향 스핀 축적을 지원하여, 올바르게 인터페이스할 경우 수직 자기 터널 접합(p-MTJ)의 무필드 스위칭을 가능하게 합니다. 이는 실질적으로 영구 자석이나 외부 필드 코일을 제거할 수 있다는 것을 의미하며, 이는 면적, 신뢰성 및 전력에 매우 중요합니다.

대칭성 외에도 Ni₄W는 0.73의 높은 SOT 효율을 제공할 수 있습니다. 유효 스핀 홀 각도 또는 댐핑형 토크 효율이라는 장점은 페르미 레벨(EF) 주변의 전자 상태에 따라 민감하게 달라집니다. 스핀 베리 곡률의 피크와 밴드 구조의 "핫스팟"은 전하에서 스핀으로의 변환을 증폭시킬 수 있습니다.

그림 2: 여러 방향으로 향하는 스핀을 강조한 Ni₄W(211)/CoFeB의 모식도. (b) Ni₄W 사면체 결정의 구조적 표현. (c) Al2O3(0001)/W(2nm)/Ni4W(30nm)/CoFeB(5nm)/캡에 대한 XRD θ-2θ 스캔. 삽입: Ni4W(211) 반사의 로킹 곡선(FWHM = 0.084°). (d) Ni₄W의 기존(평면 내) 및 평면 외 스핀 홀 각도와 주요 SOT 물질의 비교. (e) 사파이어 좌표로 표시된 동일한 스택의 상호 공간 지도 [2].

2) W 화학량론과 Co 코도핑을 통한 페르미 레벨 튜닝:

현재텅스텐 함량을 조절하는 홀 도핑과 가벼운 코발트(Co) 코도핑을 도입하여 Ni₄W의 EF를 체계적으로 튜닝하고 있습니다.

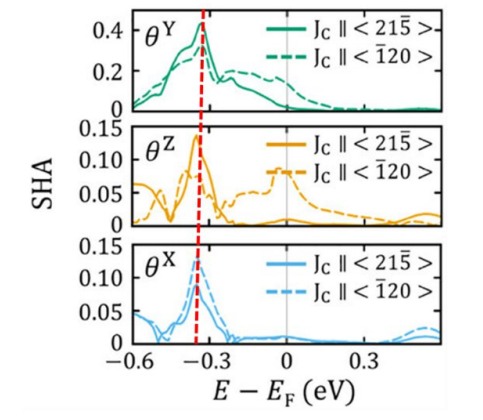

그림 3: Ni₄W(211)의 스핀 홀 각도. 녹색, 노란색 및 파란색은 θY, θZ 및 θX를 추적하며 실선과 점선은 두 개의 직교 전류 방향을 나타냅니다. 여기서 빨간색 점선은 특정 페르미 레벨[2]에서 달성할 수 있는 최고 SHA를 나타냅니다.

그림 3에서 볼 수 있듯이, 목표는(a) 댐핑과 같은 토크 효율(강자석에 전달되는 스핀 전류 증가)을 증가시키는 SHC(빨간색 점선)의 최대값에EF를 맞추는 것입니다.(b)나노초 스위칭을 위한 낮은 Jc. (c) 긴밀한 백엔드-라인(BEOL) 통합에 필요한 낮은 저항과 열 안정성을 유지합니다. 현재 글로벌파운드리는 BEOL의 M4-M5 금속 라인 사이에 22nm FDX 및 28nm HKMG CMOS 플랫폼에 STT-MRAM을 탑재하고 있습니다.

3) Ni4W 합금 및 Co 도핑 SOT 연구에 대한 저의 접근 방식:

DC 마그네트론 스퍼터링을 사용하여 사파이어 기판에 Ni₄W(211)를 증착하고 비 전통적인 스핀 성분을 최대화하는 것으로 보고된 방향을 목표로 합니다. XRD/로킹 커브 및 상호 공간 매핑은 원하는 텍스처를 보장하고, AFM 및 TEM은 인터페이스 품질을 평가합니다. 또한, 스퍼터링된 박막에서 UPS/XPS로 작업 기능과 Ni, W, Co의 조성을 모니터링합니다. 그런 다음 Py 및 CFB와 같은 강자성층을 스퍼터링하고, SOT 측정을 위해 2차 하모닉 홀 및 스핀 토크 FMR을 수행하여 댐핑 유사/장 유사 성분을 추출합니다. 또한 홀 막대와 p-MTJ를 사용하여 스위칭 확률 대 펄스 폭, 에너지 지연 스케일링 및 유지력을 정량화합니다.

4) 저대칭 웨이일 반금속 TaIrTe₄ 및 NbIrTe₄의 SOT 연구:

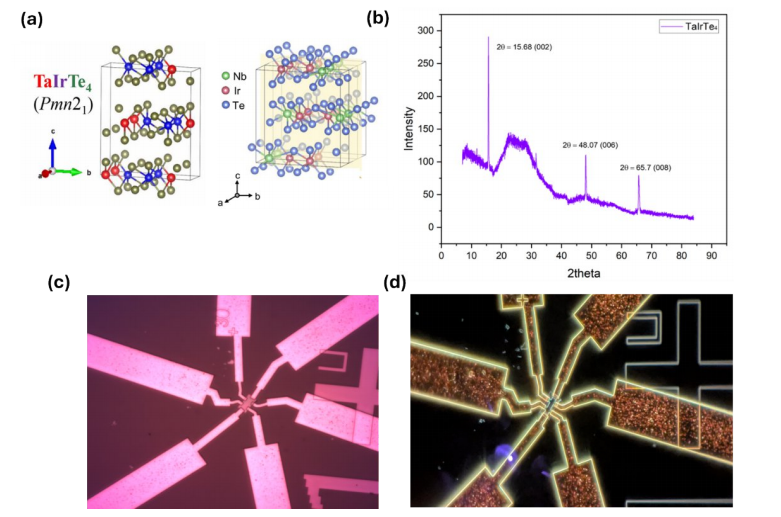

그림 4에서 볼 수 있듯이, TaIrTe₄ 및 NbIrTe₄와 같은 희소 금속 Ta 및 Nb 기반 합금, 층상 반금속은 본질적으로 낮은 결정 대칭성을 가지고 있습니다. 이러한 낮은 대칭성 덕분에 평면 내 전류에서 기존과는 다른 스핀 분극(OOP z-스핀 포함)이 가능합니다. 따라서 추가적인 대칭 차단 레이어 없이 필드 프리 스위칭이 가능합니다.

그림 4: (a) 웨이일 반금속 TaIrTe4 및 NbIrTe4의 결정 구조. (b) Co 기반 X-선 장비에서 얻은 TaIrTe4의 XRD 데이터. (c), (d) 각각 에칭 전과 에칭 후의 TaIrTe4/Py/Ru 스택의 패턴 홀 바 소자의 현미경 이미지.

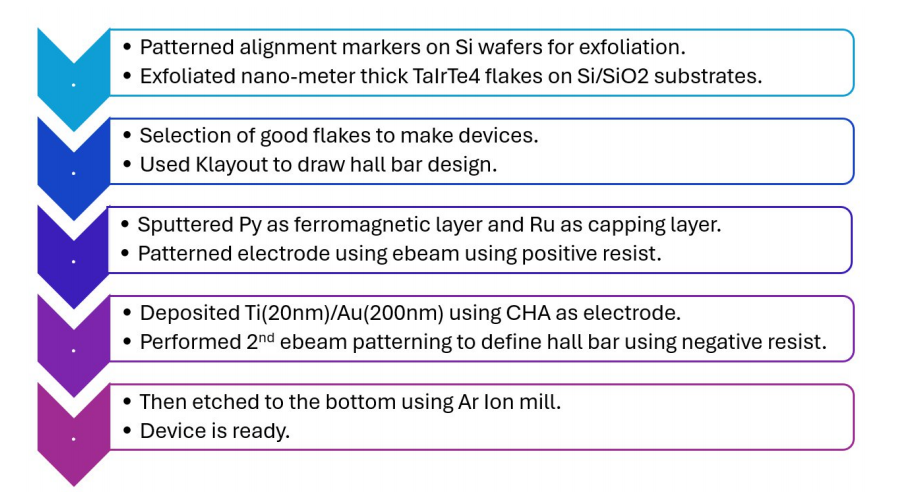

단결정에서 TaIrTe₄ 및 NbIrTe₄ 플레이크를 기계적으로 박리하여 절연성 프리패터닝Si/SiO2 기판 위에 올리고, Py 또는 CoFeB 강자성층을 스퍼터링하고 전자빔 리소그래피를 통해 홀 바에 패턴화하면 전체 공정 흐름은 그림 5에 정리되어 있습니다. 이러한 홀 바 장치를 사용하여 2차 고조파 홀을 수행하고, 단방향 스핀 자기 저항(USMR) 신호를 측정하고, 전압 제어 자기 이방성 및 전기장 효과를 변조하기 위해 정전기 게이팅(HfO₂/Al₂O₃ 유전체)을 탐색합니다.

그림 5: 2차 고조파 및 USMR 측정을 위한 TaIrTe/Py/Ru 스택 디바이스의 홀 바 제작 공정 흐름.

5) 전압 제어 자기 이방성과 같은 전압 제어 효과의 통합:

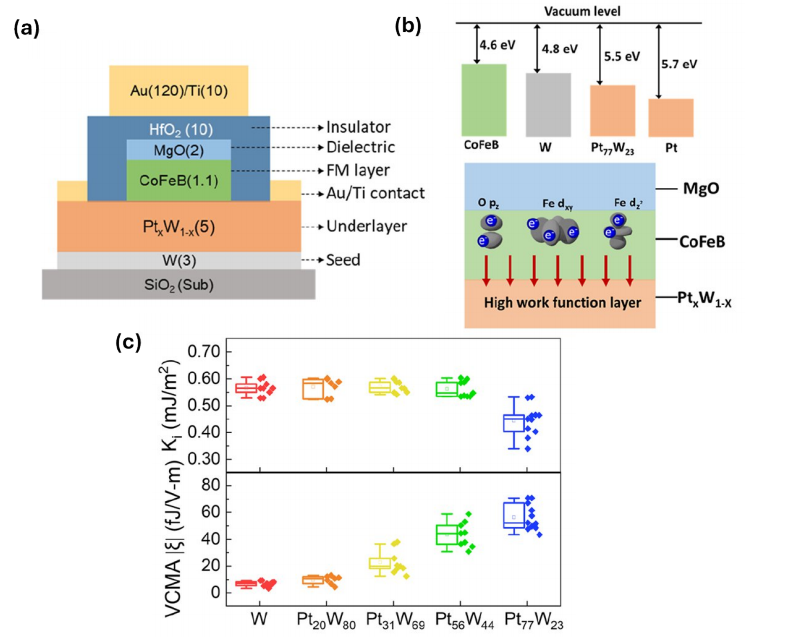

최근 연구[4]에서 그림 6에 표시된 바와 같이, CoFeB/MgO 아래의 언더레이어 작업 기능을 조정하면 VCMA를 현저하게 증폭시킬 수 있음을 보여주었습니다.W/PtxW1-x/CoFeB/MgO 스택에서 Pt 함량이 증가하면 금속의 일함수가 증가하고 평형 상태에서 CoFeB/MgO 계면이 전자 고갈되어 계면 이방성의 전기장 응답이 향상됩니다. UPS와 XPS는 일함수 이동과 계면 전하 이동을 확인합니다. Pt 함량을 조정하여 순수 W 제어보다 최대 약 8배 더 큰 VCMA 계수를 달성했으며,Pt77W23에서 최고의 성능을 보였습니다.

6) 응용 분야 및 영향:

Ni4W, TaIrTe4, NbIrTe4와같은 새로운 저대칭 소재에 대한 저의 프로젝트는업계가 캐시 및 임베디드 메모리에 SOT-MRAM을 적용하는 데 도움이 될 것입니다. 이러한 희귀 금속을 기반으로 하는 필드 프리 스택은 외부 필드를 제거하고 주변 회로를 간소화합니다. 최적화된 도핑과 결정 대칭성을 통해 비트당 에너지가 펨토줄 영역에 도달할 수 있어 데이터센터 전력 소비를 줄이는 데 직접적인 도움이 됩니다.

그림 6: (a) 게이트 홀-바 디바이스의 단면도. (b) W, Pt₇₇W₂₃ 또는 Pt와 결합했을 때 플랫 밴드 한계에서 CoFeB의 에너지 레벨 정렬 및 열 평형 상태에서 CoFeB/MgO에서 높은 일함수 PtₓW₁₋ₓ 밑층으로의 전자 공핍의 모식도입니다. (c) 언더레이어로 사용된 다양한 PtxW1-x 합금에 대한 Ki 및 VCMA의 분포도(박스형 플롯) [4].

이러한 새로운 SOT-MRAM 소자는 확률론적 컴퓨팅과 인메모리 컴퓨팅에도 사용할 수 있습니다. 펄스 폭과 게이트 전압을 통해 스위칭 확률을 제어함으로써 이러한 MRAM 소자는 최적화 및 생성형 AI 가속기에 더욱 유용한 p-비트 또는 가중 샘플러 역할을 합니다.

CMOS 기반 NVM은 우주 탐사 활동에서 방사능 문제가 있습니다. SOT-MRAM은 안전하고 방사선에 강한 전자 장치를 위한 경로를 제공합니다. 자기 비트는 소프트 오류에 강하고 희귀 금속 기반 스택은 항공 우주에 중요한 온도와 방사선에서도 견고합니다.

이러한 연구를 통해 다음과 같은 결과를 기대할 수 있습니다: (i) Ni₄W에서 SOT를 극대화하기 위한 도펀트/화학량론 맵, (ii) 박리된 저대칭 반도체의 무필드 스위칭, (iii) 신뢰할 수 있고 제조 가능한 SOT MRAM 및 확률론적 컴퓨팅을 위한 통합 경로. 보다 광범위하게는 이 프로젝트는 희소 금속(W, Ta, Nb)을 밴드 구조 수준에서 어떻게 설계하여 지속 가능하고 영향력이 큰 전자기기를 구현할 수 있는지 강조하여 기본적인 스핀트로닉스와 실용적인 메모리 기술을 모두 발전시킬 수 있습니다.

약력

브람두타 딕싯은 미국 미네소타 트윈시티에 있는 미네소타 대학교 나노 자기 및 양자 스핀트로닉스 연구소의 박사 과정3년차 연구원입니다. 그는 소자 물리학, 재료 과학, 스핀트로닉스 분야에서 6년간 업계와 학계에서 경력을 쌓았습니다. 그의 현재 연구는 다방향 SOT 소스로서의 에피택셜 Ni₄W, 토크 효율을 높이고 쓰기 전류를 줄이기 위한 W 화학량론 및 Co 코도핑을 통한 페르미 레벨 튜닝, 필드 프리 스위칭을 위한 박리된 TaIrTe₄/NbIrTe₄ 홀바 장치 등 희소 금속 스핀트로닉스에 중점을 두고 있습니다. 그는 박막 성장을 XRD/UPS/XPS, ST-FMR, 2차 하모닉 홀, AHE/USMR과 통합하고, 몇-fJ MRAM 작동을 위해 전압 제어 자기 이방성(VCMA) 및 전압 제어 교환 커플링(VCEC)을 갖춘 SOT를 공동 설계했습니다. 이전에는 GlobalFoundries에서 디바이스/통합 엔지니어(14nm FinFET, 28nm HKMG 및 40nm NVM 전반의 수율 및 공정 개선)로, Advanced Micro에서 고급 기술 검증 인턴으로 근무했습니다. Devices(AMD)(3nm 및 5nm FinFET과 같은 최첨단 노드의 방법론 및 수율 상관관계)에서 근무했습니다. 그 이전에는 독일 뷔르츠부르크 대학교에서 MBE로 성장한 HgTe/CdHgTe/Py 3D 토폴로지 절연체 스택을 연구했습니다. 미조람 대학교의 B.Tech 금메달리스트인 그는 Advanced Materials, Advanced Functional Materials, Physics Reports 및 ACS Nano에 논문을 공동 집필했습니다.

참고 문헌

[1] 딕싯, 수리아 나라인, 아르시드 니사르, 브람두타 딕싯 외. "광학 지원 초고속 스핀트로닉스: 검토." 물리학 보고서 1140 (2025): 1-46. (IF: 29.5)

[2] 양이페이, 이승준, 유치아 첸, 치 지아, 브람두타 딕싯 외. "Ni4W의 다방향 스핀 성분을 이용한 큰 스핀-궤도 토크." Advanced Materials (2025): 2416763. (IF: 26.8)

[3] 양 이페이, 이승준, 유 치아 첸, 치 지아, 브람두타 딕싯 외. "Ni4W에서 다방향 스핀 성분을 가진 큰 스핀-궤도 토크 (Adv. Mater. 32/2025)". 고급 재료 37, no. 32 (2025): e70089. (표지 페이지)

[4] 첸, 유치아, 토마스 피터슨, 치 지아, 이페이 양, 슈앙 량, 브랜든 R. 징크, 유한 황, 데이원 류, 브람두타 딕싯, 지안핑 왕.. "일-기능-설계된 Pt x W1-x 언더레이어를 통한 CoFeB/MgO 시스템에서 크고 조정 가능한 전자 공핍 기반 전압 제어 자기 이방성." ACS 나노 19, 16 (2025): 15953-15962. (IF: 16.0)

바

바

비즈 & 구체

비즈 & 구체

볼트 및 너트

볼트 및 너트

도가니

도가니

디스크

디스크

섬유 및 원단

섬유 및 원단

영화

영화

플레이크

플레이크

폼

폼

호일

호일

과립

과립

벌집

벌집

잉크

잉크

라미네이트

라미네이트

덩어리

덩어리

메시

메시

메탈라이즈드 필름

메탈라이즈드 필름

플레이트

플레이트

파우더

파우더

Rod

Rod

시트

시트

단결정

단결정

스퍼터링 타겟

스퍼터링 타겟

튜브

튜브

워셔

워셔

전선

전선

변환기 및 계산기

변환기 및 계산기

Chin Trento

Chin Trento